105 Understanding Digital Electronics

For whom intended This course is intended for individuals whose primary formal training is not in the field of electronic engineering. Digital controls and electronics are incorporated in almost every technical activity, and all technical personnel have to deal, at least to some extent, with some aspects of digital electronics.

Objectives To help participants to understand the concepts and terminology of digital electronics. It is not an in-depth digital electronics course but rather a course aimed at individuals who require an intensive review of basic principals, without the assumption of any prior knowledge of the topic. The course is fast paced and as non-mathematical as possible.

Objectives To help participants to understand the concepts and terminology of digital electronics. It is not an in-depth digital electronics course but rather a course aimed at individuals who require an intensive review of basic principals, without the assumption of any prior knowledge of the topic. The course is fast paced and as non-mathematical as possible.

Diploma Programs: This course (or Course 104/105) is required for TTi’s Electronic Design Specialist (EDS) and Electronic Telecommunications Specialist (ETS) diploma programs. It may be used as an optional course for any other TTi Specialist Diploma Program.

Related Courses: This content forms part (along with course 104) of TTi's extended course 104/105, which is available as an OnDemand Complete Internet Course. Either Course 104/105, Course 104-3 or Course 105 may be presented on-site, at your facility.

Prerequisites: There are no definite prerequisites. However, this course is aimed toward individuals involved in a technical field other than electronics. An understanding of basic algebra will be useful.

Text Each student will receive 180 days access to the on-line electronic course workbook. Renewals and printed textbooks are available for an additional fee.

Course Hours, Certificate and CEUs Class hours/days for on-site courses can vary from 14-35 hours over 2-5 days as requested by our clients. Upon successful course completion, each participant receives a certificate of completion and one Continuing Education Unit (CEU) for every ten class hours.

On Demand Most chapters of course 105 are also available as OnDemand Internet Short Topics. See the course outline below for details. Chapters priced at $50 or more include video.

Click for a printable course outline (pdf).

Course Outline

Chapter 1 - Semiconductor Physics

- Covalent Bonds

- Conduction in Semiconductors

- Semiconductor Physics

- Doped Semiconductors

- N-type and P-type Doping

- Diffusion

- Current Flow in n-type Material

- Current Flow in P-type Material

Chapter 2 - Introduction to Digital Electronics

- Digital Circuits

- Sampling and Digital Data

- Disadvantage of Digital Circuits

- Advantages of Digital Circuits

- Embedded System

- Integrated Circuit (IC)

- Logic Gates

- Truth Table

- Boolean Logic

- NAND and NOR Logic Gates

- Logic Circuits

- Synchronous Sequential State Machine

- Combinatorial vs. Sequential Digital Systems

- State Register - a set of Flip-Flops

- State Register

Chapter 3 - Analog vs. Digital

- Non-sinusoidal Waveforms

- Square Wave

- Pulse Shape of Square Wave

- Analog vs. Digital

- Analog and Digital Waveforms

- Analog vs. Digital

- Analog Waveform of Brick

- Digital Waveform

- Five Quanta Digital Waveform

- Analog and Digital Signals

- Types of Electrical Signals

- Digital Signals

- Transfer Characteristics

- Logic Levels

- Unwanted Digital Signals

- Analog-to-Digital and Digital-to-Analog Conversion

- Output Waveform of DAC

- Percentage Resolution

Chapter 4 - Diodes

- Alloy Junction Diode

- Planar Technology (Diffusing)

- pn Junction Behavior

- Junction Barrier

- Forward Biasing a p-n Junction

- Reverse Biasing a p-n Junction

- Types of Diodes

- Rectifier Diodes

- Signal Diodes

- Zener Diodes

- Simple Voltage Regulator

- Tunnel Diodes

Chapter 5 - Transistors and Biasing; Field Effect Transistors (FETs)

- Transistors

- Bipolar Junction Transistor

- Operation of an npn Transistor

- How Transistors Amplify

- Example of Amplifier Gain

- Common Emitter Amplifier

- Common Base Circuit

- Common Emitter Circuit

- Common Collector Circuit

- Amplifier Fundamentals and Considerations

- Feedback

- Negative Feedback

- Transistor Summary

- Field Effect Transistors — FETs

- Junction Field Effect Transistor (JFET)

- Channel Depletion

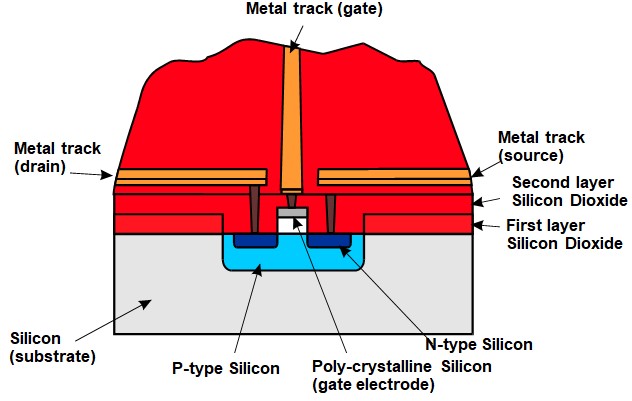

- Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET)

- n-Channel Enhancement

- n-Channel Depletion

- Transfer Characteristics

- Power FETs

- Gallium Arsenide (GaAs) FETs

- FET Audio Amplifier

Chapter 6 - Numbering Systems and Binary Arithmetic

- Numbering Systems

- Counting in Octal and Hexadecimal

- Representing Numbers Using Powers

- Decimal (Base 10)

- Binary (Base 2)

- Octal (Base 8)

- Hexadecimal

- Decimal Numbers

- Binary Numbers

- Conversions

- Octal to Decimal

- Hexadecimal to Decimal

- Octal Decimal Hexadecimal

- Binary Arithmetic

Chapter 7 - Logic Functions

- Logic Gates—Inverter

- AND Gates

- OR Gates

- NAND Gates

- NOR Gates

- XOR Gate (Exclusive OR State)

- XNOR Gates

- XOR Gates, cont.

- XOR and XNOR Gates

Chapter 8 - Boolean Algebra

- Introduction to Boolean Algebra

- Boolean Addition

- Boolean Multiplication

- Boolean Algebra Laws

- Commutative Laws

- Associative Laws

- Distributive Law

- Boolean Algebra Rules

- DeMorgan’s Theorems

- Boolean Expression for a Logic Circuit

- Truth Table from a Logic Circuit

- Standard Forms of Boolean Expressions

Chapter 9 - Karnaugh Maps

- Introduction to Karnaugh Maps

- 3 and 4 Variable Karnaugh Map

- Standard SOP Mapping

- Nonstandard SOP Mapping

- Map Simplification — SOP Expression

- Direct Mapping—Truth Table

- Don’t Care Conditions

Chapter 10 - Digital Troubleshooting

- Faults

- External Faults

- Internal Faults

- Faults—Parametric

- Faults—Logic

- Faults—Static and Dynamic

- Test Equipment

- Logic Probes

- Clip-On Indicators

- Dynamic Measurements

- Location of Faults

- Isolation of Faults

Chapter 11 - State Diagrams, Tables and Machines

- Example: Coin-Operated Vending Machine

- State Diagram for Controller

- State Table for Controller

- State Machines—Moore

- State Machines—Mealy

- State Assignment

- Binary Encoded State Assignment

- Minimized Boolean Equations

Chapter 12 - Memory

- Computer System—Memory

- Memory Terminology

- Diagram of a 32 × 4 Memory

- Memory Input and Output Lines

- Memory in a Computer

- RAM and ROM Architecture

- Address_Bus Decoding

- Memory Device

- Memory Family

- Timing—ROM Read

- Mask ROM

- An 8 × 4 ROM Array

- PROMs

- EPROM

- Memory Tradeoffs

- Flash Memory Chip

- ROM Applications

- Semiconductor RAM Family

- Static RAM Cell

- Logic Diagram of 256 × 4 Static RAM

- Static RAM Basic Organization 256 × 4

- Static RAM Basic Read/Write Cycle Timing

- Dynamic MOS RAM Cell

- Dynamic Memory Cell (Symbolic Representation)

- Basic Programmable Logic Array (PLA)

- Concept of PLA Matrix

- PLD Notation

- Architecture of PLA

- Polarity Fuse

Chapter 13 - Circuit Board Technology

- Subtractive Processes

- Additive Processes

- Single-Sided Boards

- Single-Sided Boards—Solder Mask

- Lead Through-Hole (LTH)

- Wave Soldering

- Surface Mount Technology

- Double-Sided Boards

- Multilayer Boards

- Holes vs. Vias

- Vias

- Backplanes and Motherboards

Chapter 14 - Hybrid Circuits

- Hybrid Substrates—Thick Film Process

- Thick Film Process

- Resistors

- Inductors

- Thin-Film Process

- Optical Mask and Substrate

- Tracks and Resistors

- Separated Tracks and Resistors

- Laser Trim Resistors

- Assembly Process

- Die Attachment to Substrate

- Wire Bonding

- Tape Automated Bonding (TAB)

- Flipped Chip—Solder Bumping

- Flipped Chip/Flipped TAB

- Packaging Process

- Bare Die Encapsulated in Plastic

Chapter 15 - Fabrication of Semiconductor Devices

- Integrated Circuits

- Fabrication

- P.MOS Transistor

- Pads

- Packaging

- Noise Immunity

- Power Dissipation

- Propagation Delay

- Speed-Power Product (SPP)

Appendix A - Glossary of Terms

Appendix B - Electrostatic Discharge

Appendix C8 - More about Boolean Logic

- Standard SOP Form

- SOP Logic Gate Implementation

- Binary Representation—Standard Product

- Standard POS Form

- Binary Representation—Standard Sum

- Standard SOP to Standard POS

- Truth Tables from SOP Expressions

- Standard Expressions from a Truth Table

Appendix C14 - More about Integrated Circuit Technology

- TTL and CMOS Logic Levels

- Basic Operational Characteristics and Parameters

- Noise Immunity

- Noise Margin

Appendix D - Laboratory/Workshop Safety Practice

Summary

Final Review

Award of Certificates for Successful Completion

Click for a printable course outline (pdf).

Revised 6/7/2018